Actually, when an external clock/cable is used, it’s only as a reference signal used to fine-tune the internal clock of the DAC (which is then used for D-to-A conversion) via a PLL stage on the Control Board FPGA.

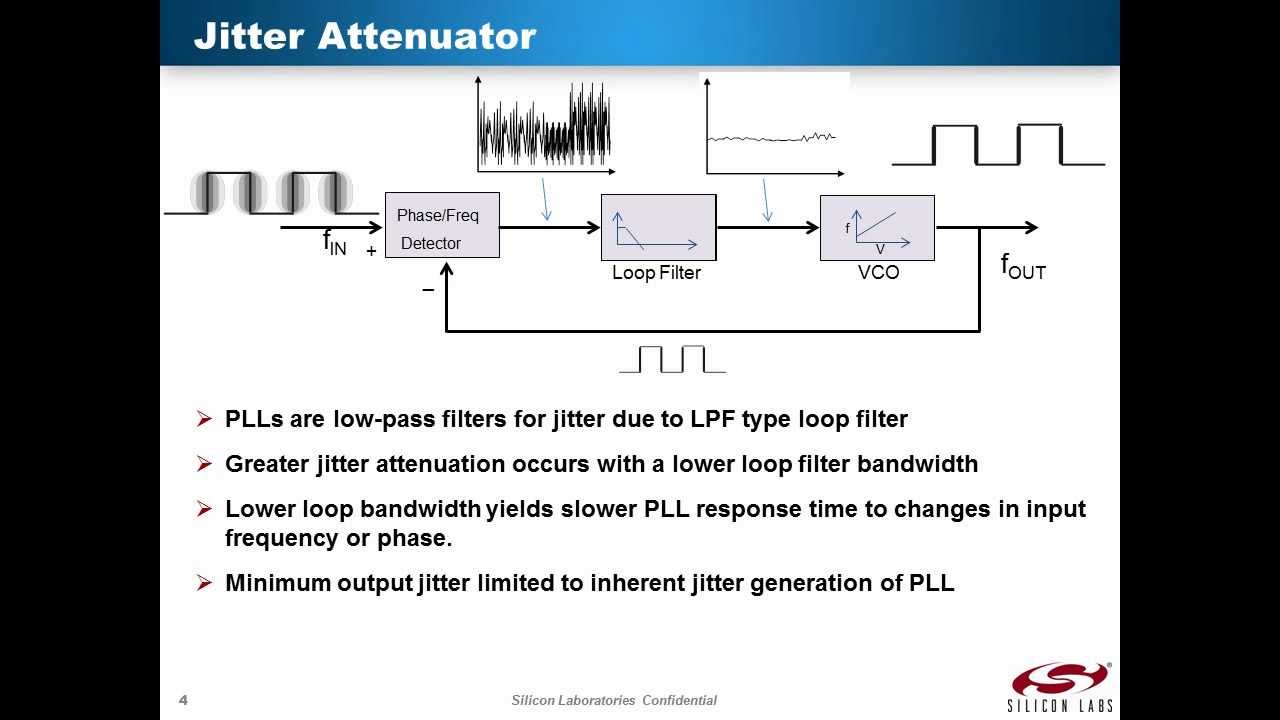

That PLL stage in fact acts as a low-pass-filter that eliminates jitter from the incoming external clock signal/cable before it’s used as a reference for the DAC’s internal clock.

So, any minute amounts of jitter caused by the cable, has no real consequence in the overall scheme of things.

James explains this clearly in his Technical Explanation posts, specifically post #51

Also, the following two videos from Silicon Labs describes clock jitter and PLLs quite well (@2:40 in Part 2 explains jitter elimination with the PLL);